# Sixth Semester B.E. Degree Examination, Aug./Sept.2020 Microelectronics

Time: 3 hrs.

1

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

#### Module-1

- a. Derive the expression of drain current of an NMOS transistor when it operates in triode and saturation regions. (10 Marks)

- b. The PMOS transistor shown in Fig.Q1(b) has  $V_t = -1V$ ,  $K'_p = 60 \ \mu A/V^2$  and  $\frac{W}{L} = 10$ . Find the range of V<sub>G</sub> for which the transistor conducts and also, in terms of V<sub>G</sub>, find the range of

$V_D$  for which the transistor operates in triode region.

#### (03 Marks)

c. An NMOS transistor has  $V_{to} = 0.8 \text{ V}$ ,  $2\phi_f = 0.7 \text{ V}$  and  $\gamma = 0.4 \text{ V}^{1/2}$ . Find  $V_t$  when  $V_{SB} = 3 \text{ V}$ . (03 Marks)

Fig.Q1(b)

# **OR 2** a. An NMOS transistor is fabricated in a 0.4 $\mu$ m process having $\mu_n C_{ox} = 200 \ \mu A/V^2$ and $V'_A = 50 \ V/\mu m$ . If L = 0.8 $\mu$ m and W = 16 $\mu$ m, find V<sub>A</sub> and $\lambda$ . Find the value of I<sub>D</sub> that results when the device is operated with an overdrive voltage, $V_{OV} = 0.5 \ V$ and $V_{DS} = 1 V$ .

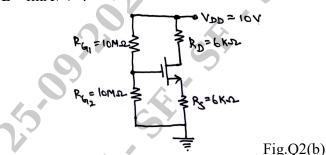

b. Analyze the circuit shown in Fig.Q2(b) and hence determine the voltages at all nodes and the currents through all branches. Neglect channel length modulation effect. Let,  $V_t = 1V$  and  $K'_n W/L = 1mA/V^2$ .

(06 Marks)

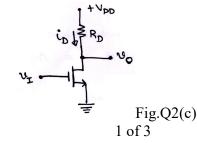

c. Sketch the transfer characteristic of the common source amplifier shown in Fig.Q2(c). Identify the segments related to three regions of operation of the device. Also, obtain the expression of incremental voltage gain,  $A_V$ .

# 15EC655

(08 Marks)

#### Module-2

- **3** a. Discuss the MOSFET biasing that uses a drain-to-gate feedback resistor. (04 Marks)

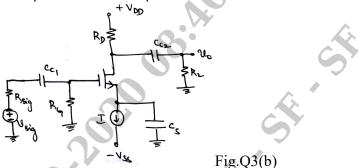

- b. For the discrete common-source MOSFET amplifier shown in Fig.Q3(b), write the equivalent circuit used to determine the low frequency response. Also, obtain the expressions of pole-frequencies of the response.

c. A drain current of 0.5 mA is observed when a gate-source voltage of 2V is applied to NMOS. Drain current increases to 0.55 mA when gate source voltage of 2.05V is applied. Find the value of device transconductance,  $g_m$ . Also obtain, threshold voltage,  $V_t$ , if  $K'_n W/L = 1 \text{ mA/V}^2$ . (04 Marks)

#### OR

4

a. Obtain T equivalent circuit model from hybrid-π model for a MOSFET. (04 Marks)

b. For the circuit shown in Fig.Q4(b), find the value of V<sub>GS</sub> such that I<sub>D</sub> = 0.5 mA. The device parameters are V<sub>t</sub> = 1V and K'<sub>n</sub>W/L = 1 mA/V<sup>2</sup>. What is the percentage change in ID obtained when the transistor is replaced by another having V<sub>t</sub> = 1.5 V? Comment on the change in I<sub>D</sub>.

(04 Marks) (08 Marks)

#### Module-3

5 a. Draw the circuit of discrete common-source amplifier with a source resistance. Derive the expressions for R<sub>in</sub>, A<sub>v</sub> and G<sub>v</sub>. (10 Marks)

b. Derive an approximate formula for 3-dB frequency,  $\omega$ H, of a direct-coupled amplifier, when a dominant pole does not exist in the gain function of amplifier. (06 Marks)

#### /OR

(08 Marks)

## 15EC655

#### **Module-4**

- Derive the expressions of input and output resistances of common-gate amplifier with active 7 a. load. (10 Marks)

- b. Draw the high frequency equivalent circuit of common source amplifier with current source as load. Analyze the same to determine 3-dB frequency, f<sub>H</sub>, using the open-circuit time constant method. (06 Marks)

- Consider CMOS implementation of common-source amplifier. Let,  $V_{DD} = 3V$ , 8 a.  $V_{tn} = |V_{tp}| = 0.6V$ ,  $\mu_n C_{ox} = 200 \ \mu A/V^2$  and  $\mu_p C_{ox} = 65 \ \mu A/V^2$ . Also, for all transistors,  $L = 0.4 \ \mu m$  and  $W = 4\mu m$ . If  $V_{An} = 20 \ V$ ,  $|V_{Ap}| = 10 \ V$  and  $I_{REF} = 10 \ \mu A$ , find the smallsignal voltage gain. (06 Marks)

- b. Obtain the expressions of output resistance, Rout, open-circuit voltage gain, Avo and shortcircuit transconductance, G<sub>m</sub>, of MOS cascade amplifier. (10 Marks)

### Module-5

- Explain the operation of passive-loaded MOS differential pair for a differential input 9 a. voltage. (08 Marks)

- Sketch the equivalent circuit of active-loaded MOS differential pair used for frequency b. response analysis. Derive the expression of transfer function. (08 Marks)

#### OR

- Obtain the expression of common-mode rejection ratio (CMRR) of passive-loaded MOS 10 a. differential pair, by considering the effect of R<sub>D</sub> mismatch. (07 Marks)

- b. Explain the operation of two-stage CMOS OP-AMP. Write the expressions of DC voltage gains, of the individual stages and the overall configuration. (09 Marks)